BCS App-a-thon – Guinness World Records Challenge

BCSWomen, part of the British Computer Society, will be attempting to break the Guinness World Record for the largest number of people learning to write Android smartphone applications at the same time on Saturday June 13th from 10.30am. They are getting together with various universities, organisations, companies and local BCS branches to get as many people as possible coding an app.

BCS App-a-thon – Guinness World Records Challenge

Imagination opens up its MIPS architecture to universities

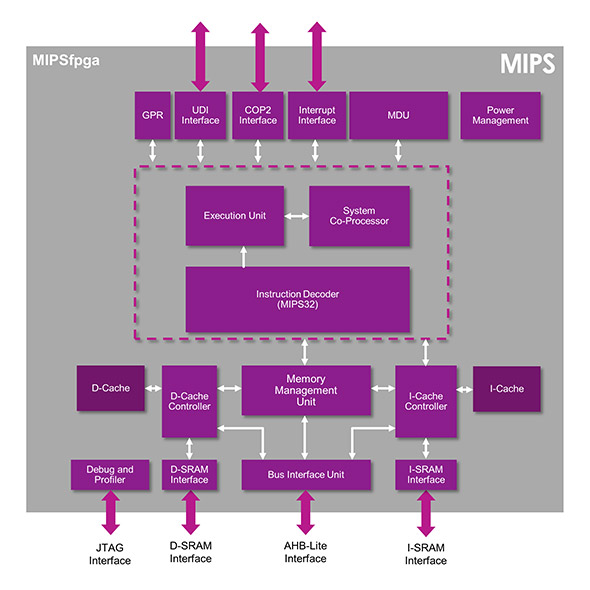

Imagination Technologies, which has two design centres in the SouthWest region, is opening up its MIPS architecture to universities with the RTL implementation of a simplified microAptiv design.

MIPSfpga gives universities around the globe free and open access to a fully-validated, current generation MIPS CPU in a complete teaching package that can be run in a low cost FPGA. The core is already popular in the PIC32MZ microcontroller from Microchip Technology but access to the detailed RTL – the code that implements the core – can be tremendously helpful for teaching.

CPU architecture is generally taught as part of electronic engineering, computer science and computer engineering courses. Until now, what’s been missing from all of these courses is access to real, un-obfuscated RTL code that will enable professors and students to study and explore a real CPU. RTL code is often hidden, or obfuscated, to prevent it being copied and used in other designs without paying royalties or license fees to the original developer.

The MIPS architecture was originally developed at Stanford University in the early 1980s. It has been the teaching architecture of choice for decades because of its elegant true RISC design, epitomized by Dr. David A. Patterson and Dr. John L. Hennessy in their book, ‘Computer Organization and Design’, now in its fifth edition.

The MIPS CPU is being offered as part of a complete free-to-download package for universities, together with a Getting Started Guide, teaching guide for professors, and examples designed to enable students to see how the CPU works and explore its capabilities. With the materials, students can develop a CPU and take it through debug, running on an FPGA platform.

This MIPS CPU configuration is designed to run on a low-cost FPGA platform, with guides available for the Digilent Nexys4 platform with a Xilinx Artix-7 FPGA, and the Terasic DE2 platform with an Altera Cyclone FPGA.

MIPSfpga is already running in several academic institutions including Harvey Mudd College, Imperial College London, University College London (UCL), and the University of Nevada, Las Vegas (UNLV).

The MIPSfpga CPU and related materials are available for download from the Imagination University Programme website now for first phase users via an application process. Academics can register at http://community.imgtec.com/university.

Phase two, starting in June, will require only a simple click-through agreement. Additional teaching materials are being developed and will be made available later this year.

However, the programme is not entirely open source. For academic users the license is simple: you can use it as you wish, but you cannot put it into silicon. If you modify it, you must talk to Imagination first if you wish to patent the changes. In summary, universities can go as deep as they like under the hood to explore how today’s complex CPUs are built.

Related articles

Headline speakers for Venturefest announced

Venturefest has announced the headline speakers for the event on 9th June, with Col Needham, founder and CEO of the Internet Movie Database (IMDb) and Scott Wilcox, the Director of Technology for SXSW Eco.

Col and Scott will be part of a Thought Leadership Conference at Venturefest in the Passenger Shed at Bristol Temple Meads which will highlight the latest developments on key issues affecting innovators and investors.

Col Needham founded IMDb 25 years ago in Bristol before it was acquired by Amazon in 1998. He continues to serve as the founder and CEO of IMDb and is now a key figure in the global film industry.

Scott Wilcox, who has firmly established South by South West Eco as the international conference on the future of sustainability, will be presenting his insights into the latest US and international green technology developments and outlining the opportunities for entrepreneurs in the region. This is a key part of Bristol’s role as the Green Capital of Europe this year.

For further information visit our Venturefest website or follow on twitter @venturefestbb

Rolls Royce transition shows power of high tech

Former ARM CEO Warren East takes over at Rolls Royce in July

The appointment of Warren East, former chief executive of chip designer ARM, to head up Rolls Royce demonstrates a key shift in the importance of the high tech industries.

The successor to John Rishton, CEO from 2011 to 2015, came from an extensive international search and shows the importance of microelectronics and embedded software to Rolls Royce which has a large aerospace base in Bristol. The company doesn’t really sell engines, even though it has a £73bn order book for them – it leases many of them and sells ‘time in the air’ instead. This has meant an increasing reliance on monitoring the engines with sensor technologies, security and global software management. All this maps directly onto the skill set of executives like Warren East. As CEO of ARM Holdings from 2001 to 2013 he helped ARM become one of the world’s leading developers of semiconductors with an outstanding record of innovation and a strong commitment to R&D.

Ian Davis, Chairman of Rolls-Royce, said: “I am very pleased that Warren East will become the new Chief Executive of Rolls-Royce following John Rishton’s retirement. Warren has an outstanding record as CEO of ARM Holdings. He is an engineer by training; he has a deep understanding of technology and of developing long-term partnerships. He has proven strategic and leadership skills in a global business and a strong record of value creation.

Warren East said: “I am delighted to be appointed as Chief Executive of Rolls-Royce. It is well positioned in growth markets, with world class engineering skills and a proud record of innovation and delivery. I have a strong desire to return to an executive position with the energy and enthusiasm a role like this demands. The markets which Rolls-Royce serves and the technology it deploys are fascinating. ”

As well as being a Non-Executive Director of Rolls-Royce, Warren East serves as a Non-Executive Director on the Boards of BT, De La Rue, local engineering company Dyson, US memory chip maker Micron and the UK’s Digital Catapult. His intention is to stand down from all but one of his current roles as a Non-Executive Director, in line with Rolls-Royce company policy.

Rolls Royce employs over 54,000 people in more than 50 countries, with over 15,500 of these being engineers. It also has a Land & Sea division for Marine, Nuclear and Power Systems, where projects such as unmanned, autonomous ships are being developed. In 2014, Rolls-Royce invested £1.2 billion on research and development and supports a global network of 31 University Technology Centres. There are over 1,000 Rolls-Royce STEM (Science, Technology, Engineering and Maths) ambassadors who are actively involved in education programmes and activities, and the company has a target to reach 6 million people through its STEM outreach activities by 2020.

East will be paid £925,000 with share incentives up to £1.6m. While at ARM he had a salary of £500,000 but is reported to have left ARM with 450,000 shares worth £4 million from the group’s long-term incentive plan and deferred annual bonus plan.

Related articles

FreeRTOS moves onto Tensilica processors for wearables and IoT

One of the world’s most popular real time operating systems is developed and supported in Bristol and has now been ported to a highly configurable high performance processor for applications in wearable designs and the internet of things (IoT).

FreeRTOS is a popular, scalable, easy-to-use real-time kernel designed specifically for small, low-power embedded systems. According to a 2013 market share study from UBM Tech, FreeRTOS had been selected for 13 percent of embedded projects that utilize an embedded operating system (OS), and is a very popular option for microcontrollers as well as smaller 32-bit processor cores. It has now been ported onto the Tensilica family of configurable processors from Cadence Design Systems. The Tensilica cores are configured from a software tool so they are optimised for a particular application with no wasted resources and can be easily integrated into a System-on-Chip design. The tool also generates the software development environment for the particular core.

“The availability of FreeRTOS on Tensilica processors and DSPs means that Cadence customers now have the option to join the many developers worldwide who already benefit from the ease of use and bullet-proof reliability of FreeRTOS. We look forward to welcoming Tensilica users to our global community,” said Richard Barry, FreeRTOS developer and principal engineer of Real Time Engineers Ltd. FreeRTOS makes it easier for programmers to develop complex real-time software that combines control and DSP threads, and FreeRTOS has specific support for Internet of Things (IoT) applications that helps customers get to market faster. Tensilica processors and DSPs are ideal for wearables and other IoT applications that combine wireless digital signal processing with control. By combining digital signal processing and control, designers can develop lower power, more efficient chips.

UltraSoC taps region for new chief exec

UltraSoC, the Cambridge-based developer of advanced debugging and analytic technology for embedded systems, has appointed Rupert Baines as its new CEO.

Baines, a Bath-based 30-year veteran of the global semiconductor and communications industries, has previously held senior roles in both start-ups and prominent trans-national companies. Most recently he was VP of Strategic Marketing at Mindspeed in Bath following that company’s acquisition of Picochip (now part of Intel), where he had served as VP of Marketing. His CV also includes spells at first:telecom (acquired by Atlantic Telecom for $818 million), Arthur D Little and Analog Devices, where he played a key role in the development and mass-market adoption of digital subscriber line (DSL).

“UltraSoC has a great team and game-changing technology,” said Baines. “We’re not only empowering designers to create better products ‘first-up’, more quickly and easily – we’re also giving them the opportunity to use connectedness and analytics to refine the performance and features of those products when they’re actually in use. This really has never been possible before.”

UltraSoC’s core offering embeds debug and analysis capabilities into the silicon chips that are used in today’s electronic products. This allows chip designers to design and debug their devices more quickly, and to offer their customers innovative features such as in-service power consumption optimization, self-testing and failure detection.

“Rupert has an outstanding track record of success in leadership and category definition in technology markets,” said Chris Gilbert, Chairman of the UltraSoC board and formerly CEO of Swindon-based Ubiquisys, acquired in 2013 by Cisco in a $310m trade sale. “We believe his passion and ability to translate great technology into real-world impact are exactly what’s needed to take UltraSoC to the next level of success.”

UltraSoC’s VC investors include Octopus Investments, whose Ventures team has helped build global businesses such as Zoopla Property Group, Secret Escapes, SwiftKey, graze.com and YPlan.